디지털 논리회로

논리 게이트

rabbit-jun

2025. 4. 5. 20:44

기본 논리 게이트

1. AND 게이트

- 두 개 혹은 그 이상의 입력 신호들에 대하여 AND 연산을 수행하고 결과 신호를 출력하는 게이트

- 두 입력 파형들에 대한 AND 게이트의 출력 파형

2. 3-입력 AND 게이트

OR 게이트

- 두 개 혹은 그 이상의 입력 신호들에 대하여 OR 연산을 수행하고 결과 신호를 출력하는 게이트

두 입력 파형들에 대한 OR 게이트의 출력 파형

3-입력 OR 게이트의 입출력 파형

NOT 게이트 (인버터)

- 입력 신호의 반전(invert)된 신호를 출력하는 게이트

- 입력 파형에 대한 NOT 게이트의 출력 파형

- NOT 게이트(Inverter)는 단일 입력에 대한 반전 기능을 수행하지만, 회로 설계도(회로도)에서는 버퍼(Buffer)와 유사한 구조를 가지기 때문에, 논리 기호 또는 실제 회로에서 버퍼 심볼에 작은 원(circle)을 붙여 표현하는 경우가 많다.

- 버퍼는 입력을 그대로 출력하는 소자

NAND 게이트와 NOR 게이트

1. NAND 게이트

- AND 게이트와 반대되는 출력을 발생하는 게이트

- 내부 회로는 AND게이트 보다 더 간단

- NAND 게이트를 이용하여 다른 게이트 구성 가능하며 만능 게이트(universal gate) 라고도 부름

AND 회로를 실제로 구현할 때 NAND + NOT으로 구현한다

논리적으로 설명할 떄

실제 회로 구현 방법

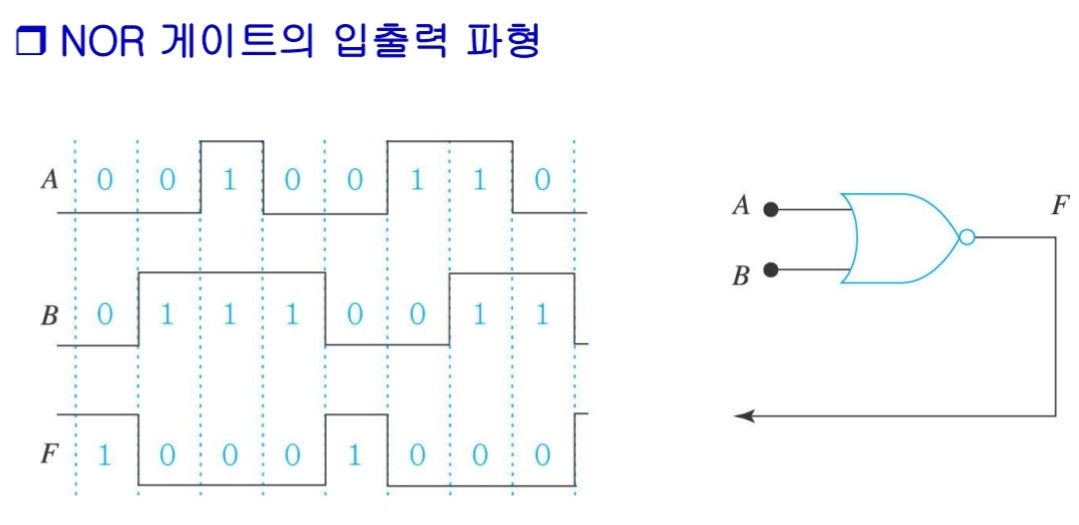

2. NOR 게이트

- OR 게이트와 반대되는 출력을 발생하는 게이트

- 내부 회로는 OR 게이트 보다 더 간단

- NOR 게이트를 이용하여 다른 게이트 구성 가능( 만능 게이트라고도 부른다)

- 논리적으로 설명할 떄

- 실제 회로 구현 방법

Exclusive-OR 게이트

1. XOR 게이트

입력 값들 중에서 1의 개수가 홀수일 때 출력이 1이 되는 함수 (홀수 함수)

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

2. Exclusive-NOR 게이트 (XNOR 게이트)

- 입력값들 중에서 0의 개수가 짝수일 떄 출력이 1이 되는 함수 (짝수 함수)

- 동등 회로(equivalence circuit)라고도 한다

논리 게이트의 내부 회로

- 논리 게이트는 전자회로 소자들(트렌지스터, 다이오드, 저항, 등)을 이용하여 반도체 칩에 제조

- 구현에 사용되는 소자들에 따른 계열(family) 분류:

- $ V_{CC} = V_{OD} = 5V $

- RTL(Resistor-Transisor Logic)

- DTL(Diode-Transistor Logic)

- TTL(Transistor-Transistor Logic)

- MOSFET(Metal-Oxide Semiconductor Field-Effect Transistor)

- CMOS(Complementary Metal-Oxide Semiconductor)

1. 트렌지스터(transistor, bi-polar junction transisor)

- 입출력단자: 콜렉터(collector: C), 에미터(emitter: E), 베이스(base: B)

- NPN 트렌지스터: 에미터 < 베이스 < 콜렉터 순으로 전압이 높음

- PNP 트렌지스터: 콜렉터 < 베이스 < 에미터 순을 전압이 높음

- 베이스와 에미터 사이에는 약 0.7v 가 필요하다

2.RTL 및 DTL 게이트 회로

- RTL 스위칭 회로: 저항(resitor) 및 NPN 트랜지스터로 구현

- $ V_{BE} $ threshold voltage(0.6V ~ 0.7V)이상이 되면, 베이스전류( $ I_{B} $ ) 가 흐르기 시작

- $ V_{BE} $가 논리적 "1"을 나타내는 +5V라면, 트랜지스터는 포화(saturation)영역에 들어가게 되어 콜렉터와 에미터 사이에 전류( $ I_{C} = V_{CC}/R_{C} $ )가 흐름 콜렉터와 에미터가 서로 접속되어 있는 전도(conduction)상태가 됨 (turn on)

- 논리연산회로에 사용될 때는 베이스 전압이 논리적"0"을 나타내는 0V 혹은 논리적 "1"을 나타내는 +5V만 인가 되기 때문에 차단상태 (turn off) _혹은 전도(포화)상태가 됨_

인버터(NOT) 기능 수행

3. NAND 게이트의 RTL 구현

- 저항은 면적을 많이 차지 하기 때문에 저항을 사용하는 회로는 잘 사용 안한다.

- 두개의 NPN 트랜지스터를 직렬로 접속하여 구성

NAND의 출력단에 스위칭 회로 접속(NOT 게이트)시키면 AND 게이트가 된다

4. NOR 게이트의 RTL 구현

- 두 개의 NPN 트랜지스터를 병렬로 접속하여 구성

NOR의 출력단에 스위칭 회로 접속(NOT 게이트)시키면 OR 게이트가 된다

DTL 게이트 회로 (Diode Trangister Logic)

- 다이오드와 트랜지스터를 이용해 구현

- 다이오드의 특성:

- 애노드(anode: A)와 캐소드(cathode: C)로 구성

- 애노드와 캐소드 간의 전압( $ V_{AC} $ )이 정방향으로 걸리면 전류가 흐름(전도 상태)

- 애노드 측의 전압이 더 높음

- $ V_{AC} $가 0V 혹은 역방향으로 걸리면 전류가 흐르지 못함(차단 상태)

- 애노드 측 전압이 더 낮음

- 애노드 측 전압이 더 낮음

1. NAND 게이트 회로

TTL 게이트 회로

- 회로 안정성 향상을 위하여 트랜지스터들만으로 회로 구현

- 소규모 반도체 IC(SSI) 칩으로 제조1. NAND 게이트 회로

2. 표준 TTL 게이트 IC칩의 특성

- 반도체 칩에 집적 시킬 떄 면적을 많이 차지하기 떄문에 소규모인 SSI칩으로 제조

7400: 네 개의 2 입력 NAND 게이트7408: 네 개의 2 입력 =AND 게이트7432: 네 개의 2 입력 OR 게이트

질문

1. 그럼 지금은 어떤 디지털 회로를 주로 사용하는가?

- RTL → DTL → TTL → CMOS로 발전해왔으며 현재는 CMOS가 주로 사용됨

반응형